研究紹介

電子デバイス計測

私達の研究室では、SNDMを用いた半導体材料やデバイスの評価技術についての研究も行なっています。SNDMを使うと半導体を何故測れるのか、何が分かるのかを紹介したいと思います。

半導体とは

まずは半導体について復習しましょう。物質にはいろいろな分類がありますが、電気の流しやすさ(導電率)に注目すると流し易い順に

- 金属

- 半導体

- 絶縁体

に分けられます。なんとも中途半端な物質ですが、この“中途半端”な物質なしに皆さんが持っているパソコンや携帯電話、スマートフォンは存在しません。半導体の最も重要な性質は、導電率を自在に変化させることができるという性質です。この性質を応用して、電気の流れを機械的なスイッチに頼ることなく自在に制御することで、コンピュータを始めとする電子機器は動作しています。

半導体で電子の流れを制御する部品は一般的に半導体デバイスとか電子部品などと呼ばれます。最も有名なものはダイオードとトランジスタです。半導体デバイスを実現する上で非常に重要なのがn型半導体とp型半導体です。n型半導体とは電子が豊富で電気伝導が電子に支配されている半導体で、p型半導体はホールが豊富で電気伝導がホールに支配されている半導体です。半導体デバイスが正しく動作するためにはn型半導体とp型半導体が適切に配置されている必要があります。私達が研究しているSNDMを使うと半導体デバイス内のn型半導体とp型半導体の分布を詳細に分析することが可能です。「測るだけってなんか地味だな」と思う人も居るかもしれませんが、半導体デバイス内のn型・p型の分布を測る技術はデバイス開発において非常に重要な要素です。デバイス開発においては常に「正しく作られているのか」とか、「正常に動作しない原因は何か」といった問題がついて回ります。このような疑問を解決するには直接構造を測ってしまうのが近道です。特に、近年のCPUやメモリに代表される大規模集積回路(LSI)の内部の構造は非常に微細で、トランジスタ1つの寸法は20nm程度です。ここまで小さくなると測定は非常に難しくなります。SNDMはこのような微細なデバイスの構造を分析できるポテンシャルをもっています。

SNDMで半導体を測る原理

SNDMが容量の電圧に対する応答を測るプローブ顕微鏡だということはSNDMの説明で分かっていただけたと思います。半導体の静電容量も電圧によって変化するためSNDMで測定が可能です。図1のような、絶縁物を電極とp型半導体で挟んだキャパシタを考えましょう。図1(a)の場合には、静電容量Cは

と表されます。ところがこれに正電圧を印加すると、正電荷を持つホールは電極1から反発されて遠ざかり、電極1の下にホールが存在しない領域(空乏層)が出来上がります。この部分は絶縁体と同じなので、静電容量Cは

と表されます。つまり、電圧を印加したことで静電容量が小さくなったわけです。n型の場合はキャリヤが負電荷を持つ自由電子なのでこの逆で、負電圧を印加すると容量が小さくなります。

図1:MOSキャパシタ

単にn型・p型というだけではなくて、キャリヤの濃度(n型なら自由電子の濃度、p型ならホールの濃度)を知ることも可能です。濃度は電圧に対する容量の応答の強さに影響を与えます。濃度が高くなるほど半導体は金属に近くなるため容量の変化は小さくなります(金属電極で誘電体を挟んだ理想的なキャパシタに近づくと考えれば納得しやすいと思います)。このように、電圧と容量の関係を調べるとn型・p型など半導体の性質を知ることができます。このような測定をCV測定と呼び、半導体の分野では一般的な測定で、半導体デバイスの教科書等をみれば必ず載っています。教科書などで紹介されている典型的なCVカーブを図2に示しました。

図2:典型的なCVカーブ

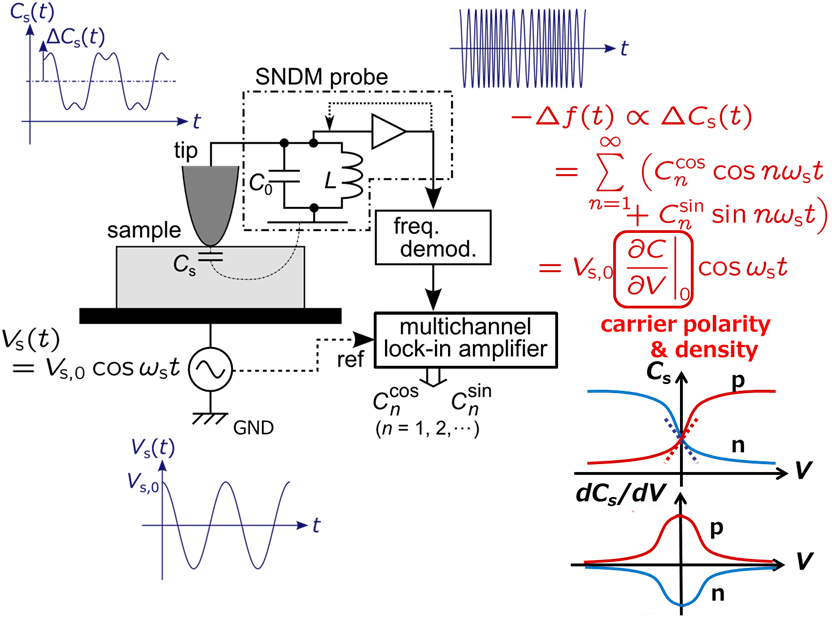

さて、SNDMで行う測定は基本的にはCV測定です。ただしSNDMの場合は、図1の電極を図3のように鋭い金属探針に置き換えて極めて微小な領域のCV測定を行います。但しSNDMの場合、容量Cを測定するわけではなく、試料に交流電圧を印加することで容量の電圧に対する応答(dC/dV)を測定します。図2から分かるように、dC/dVの符号と大きさは半導体のキャリヤの極性と濃度に対応するので、SNDM像からp型・n型の分布を知ることができます。

図3:探針を用いた微小領域のC-V測定

SNDMによる半導体デバイス評価の例

当研究室で半導体デバイス評価に関して行なっている主な研究は

- デバイス内のn型・p型の分布の測定

- Flashメモリに蓄積された電荷分布の測定

- SiC半導体デバイスのキャリア分布測定

- 2次元電子ガスの計測

- シリコン単結晶太陽電池の計測

- 超高次走査型非線形誘電率顕微鏡法(SHO-SNDM)

- 局所DLTS法によるMOS界面トラップの分布計測

- 原子層(2次元)半導体のキャリア分布観察

に分けられます。それぞれについて結果の一部を交えて紹介します。

デバイス内のn型・p型の分布の測定

これは前の節で説明した内容そのものです。半導体デバイスを切断して、図4に示したように断面をSNDMで測定します。図5は実際にトランジスタの断面を測定したものです。スケールを見ていただければ分かる通り100nmにも満たない小さなトランジスタですが、その構造が明瞭に可視化されています。

図4:デバイス断面のキャリヤ分布測定

図5:FET断面のSNDM像

Flashメモリに蓄積された電荷分布の測定

この項目は、前の項目と随分違って見えるかもしれませんが、CV測定を行うという点は変わりません。

測定の話に入る前にまず、Flashメモリについて簡単に説明しておきます。Flashメモリという名前はみなさんが使っているUSBメモリやパソコンのSSDに使われているためご存知の方が多いと思います。また、今挙げた用途から分かるように、Flashメモリは電源を切ってもデータが消えない(不揮発性)メモリです。Flashメモリは1つ1つのメモリセルに電荷を閉じ込めることで情報を記憶します。すると、その下にあるトランジスタのゲートに電圧がかかった状態になり、トランジスタの動作点が変化します。そのため各メモリセルに電荷が在るか無いかを判別できます。そのため、メモリセルにどのように電荷が蓄えられているかがメモリの動作に重要で、蓄積された電荷の分布を測定することはメモリの性能を向上するために重要と言えます。

少し前置きが長くなりましたが、測定の話に戻ります。この測定ではデバイスの断面を測定するのではなく、図6に示したように上から測定します。電荷が蓄積されているメモリセルでは、蓄積されている電荷が下の半導体層に電界を及ぼすためCVカーブが変化します(半導体デバイスの教科書を見ると酸化膜内の固定電荷がMOSの特性に与える影響が書かれていると思いますが、それと同様の効果です)。この変化を検出することで蓄積されている電荷の極性と量、分布を知ることができます。図7は測定結果の一例です。蓄積された電荷の存在が鮮明に映し出されています。

図6:Flashメモリの蓄積電荷分布の測定

図7:MONOS型Flashメモリにおける蓄積電荷分布の測定結果[1]

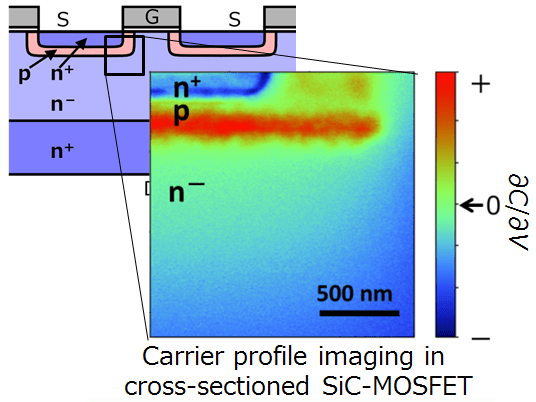

SiC半導体デバイスのキャリア分布測定

SNDMで分析可能なのはSi半導体デバイスだけではありません。一般に測定が難しいと言われている材料も高い静電容量感度のおかげで測定可能です。炭化ケイ素(SiC)半導体デバイスのキャリア分布を可視化した例を紹介いたします。

図8:縦型SiC-MOSFETの断面測定の結果

ここまでは電気的に静止したデバイスのキャリア分布測定でしたが、ゲート・ソース間に電圧を印加したときの挙動を可視化することもできます。ゲート・ソース間に100 Hz程度の交流電圧を印加して状態で図9において赤枠で囲まれた領域を測定し、キャリア分布のゲートバイアス依存性を測定しました。図10は結果を動画で表示した例になります。

図9:断面キャリア分布のゲートバイアス依存性測定エリア

図10の左上に表示されている数値はゲート・ソース間電圧です。この例では赤い領域がp型の領域、緑の領域がn型の領域を表しています。ゲート・ソース間電圧に応じてキャリア分布が変化している様子を可視化することができました。ここで紹介した例ではFETがオンする(チャネルが形成される)までは見えていませんが、文献2にチャネル形成までを可視化した結果が掲載されています。

図10:断面キャリア分布のゲートバイアス依存性測定の結果

2次元電子ガスの計測

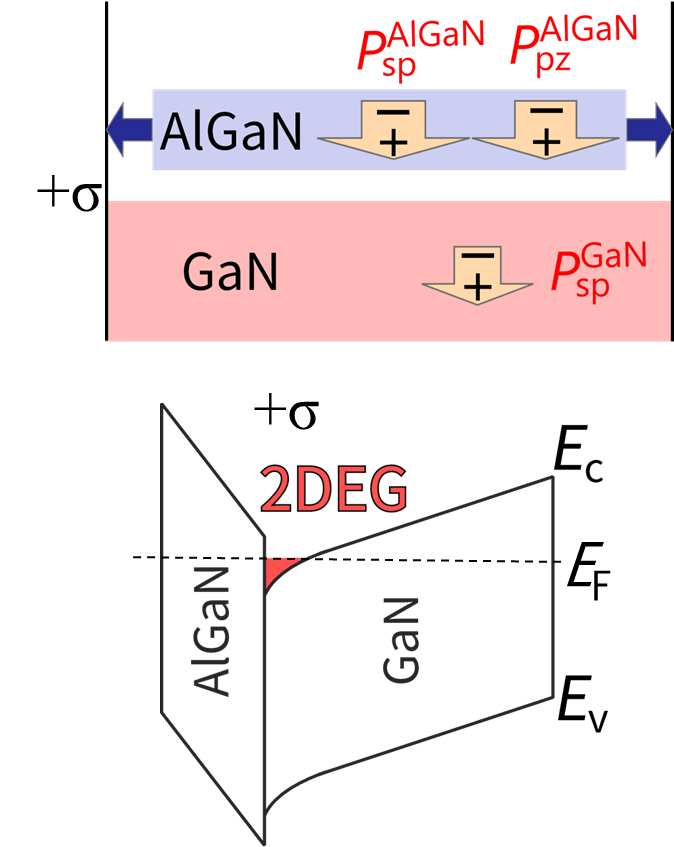

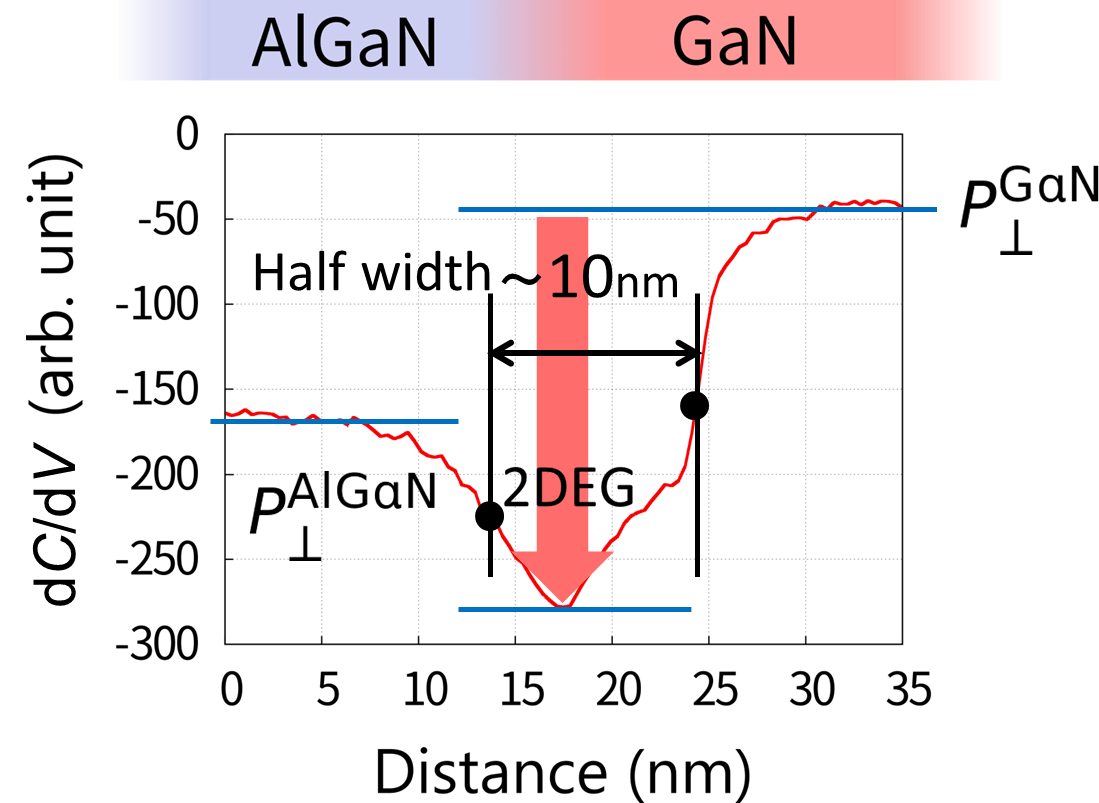

AlGaN/GaN ヘムト(high-electron mobility transistor)はハイパワー、高周波デバイスとして期待されている。AlGaN/GaNヘテロ構造の界面にはそれぞれの材料中の分極の不連続を補償するように2次元電子ガスが湧き出しこの2次元電子ガスをキャリアとした高電子移動度のトランジスタが実現されている。この2次元電子ガスの厚さは非常に薄く、今までそれを実空間で観測するのは難しかった。一方SNDMはその静電容量変化に対する高感度性を生かして2次元電子ガスのみならず分極も高S/N比で観測可能ある。下図にAlGaN/GaNヘテロ構造の概念図並びにSNDMで計測した分極及び2次元電子ガスの一次元プロファイルを示す。

図11:lGaN/GaNヘテロ構造の概念図。図中EC, EV,及び EFはそれぞれ伝導帯端、価電子帯端及びフェルミレベルを示す。また +σはAlGaN/GaN 境界での分極の不連続分に相当するシート電荷である

図12:計測されたAlGaN/GaNヘテロ構造のSNDM信号のプロファイル

シリコン単結晶太陽電池の計測

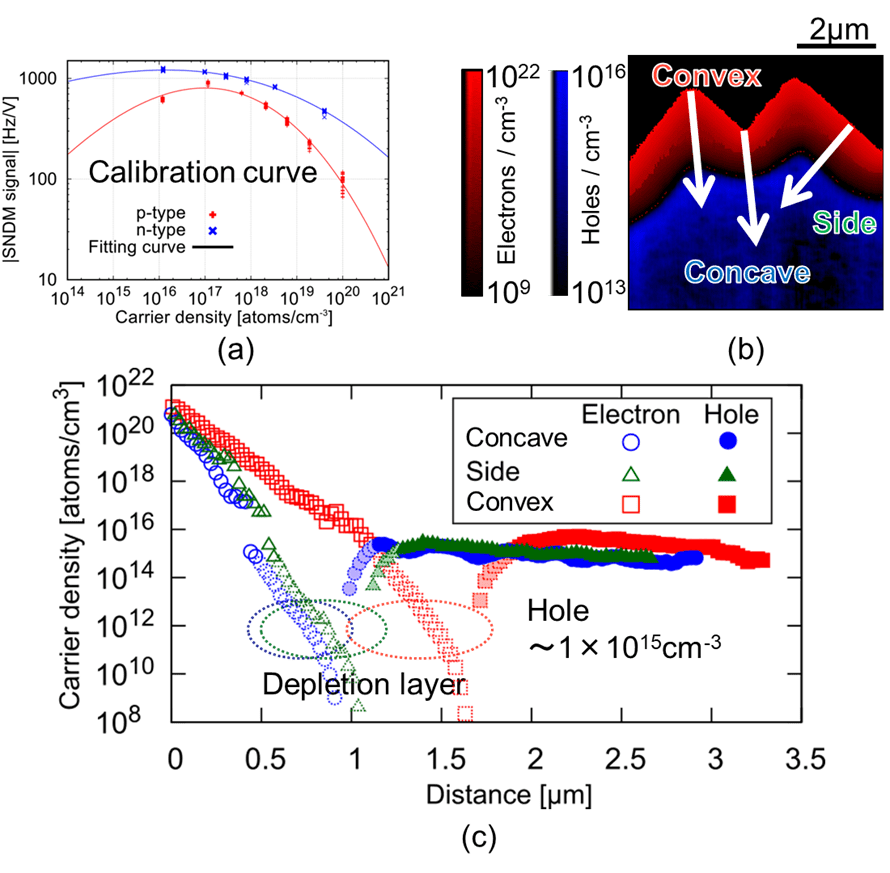

シリコン(Si)太陽電池の発電効率はエミッタ中のドーパント分布に大きく左右される。しかし太陽電池のエミッタは光の吸収効率を上げるためピラミッド状のテクスチャ構造をとるためそのドーパント分布を観測することは難しいとされていた。そこでSNDMを用いてシリコン太陽電池のエミッタ中のドーパント(キャリア)分布を計測してみた。この計測には SNDM(dC/dV)法及びキャリア濃度に対する信号強度の一価関数性が保証されているdC/dz-SNDM法を相補的に用いた。階段状のドーパント濃度分布を持つ標準サンプルと太陽電池の断面サンプルを同時にCMP研磨し、そのデータを比較することによりエミッタ中のキャリア濃度の定量評価を行った。その結果を図13にまとめて示す。これらは3次元のテクスチャ構造をしているエミッタ中のキャリア濃度を定量的に計測した最初の計測例である。

図13:(a)標準サンプル中のキャリア濃度とSNDM信号の関係を示す校正曲線。(b)エミッタ中のキャリア濃度の定量2次元分布。(c)キャリア分布のラインプロファイル

超高次走査型非線形誘電率顕微鏡法(SHO-SNDM)

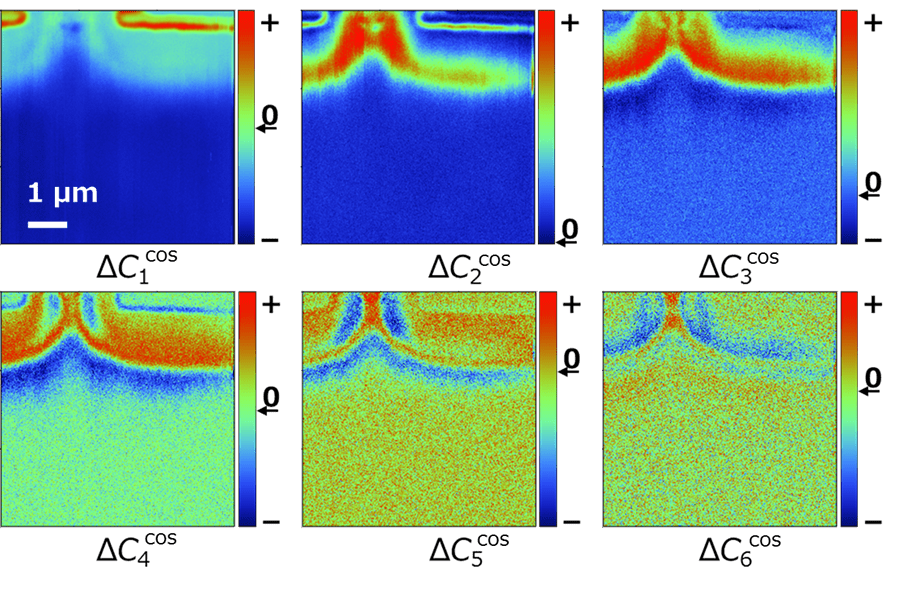

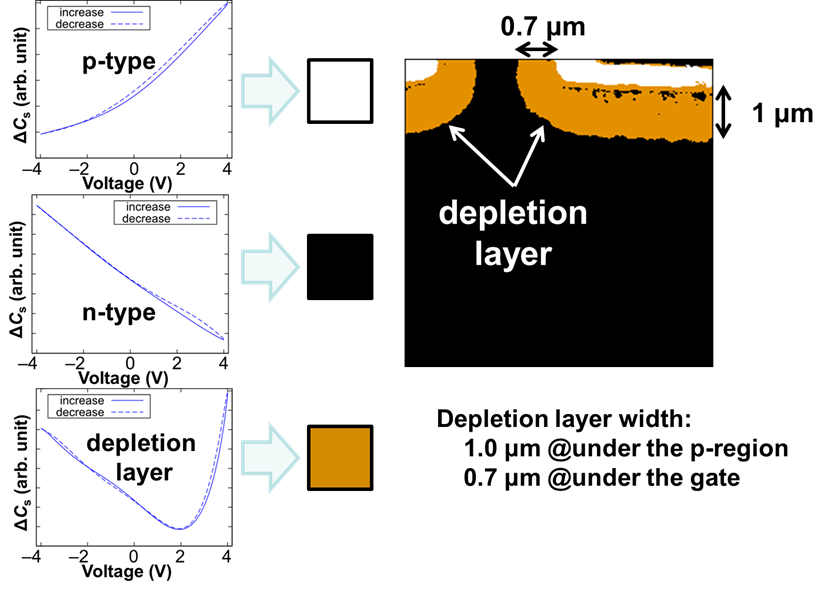

近年dC/dV信号のみならずその高次項まで取得し半導体材料やデバイスに関する多くの物理情報が得られる超高次走査型非線形誘電率顕微鏡法(SHO-SNDM)が開発された。本手法を用いると計測ピクセル毎に局所的なC-V曲線を得る事が出来、半導体の極性や空乏層の分布計測が簡単にでき、更にMOS界面計測に適用すると膜内にトラップされたキャリアやDitの分布計測が可能になる等その解析能力が格段に向上する。その原理図をSNDMの基本原理図と共に図14に示す。SHO-SNDM法を行う場合にはマルチチャネルロックインアンプを用い基本波から高調波迄(通常6倍波迄)取得し非線形容量変化を取得する。更に時間を媒介変数に取りΔC-V曲線をピクセルごとに再構成する。本手法を用いSiC-DIMOSFETの断面計測を行った。各高調波像を図15に示す。これらのデータは各ピクセル毎の高調波成分の大きさを示しており、これを用いてピクセル毎にC-V曲線を再構成した。C-V曲線の形が単調増加であればそのピクセルはp型、単調減少であればn型、V型であれば空乏層と判定され、結果図16に示すような空乏層分布像を得る事が出来る。

図14:走査型非線形誘電率顕微鏡と超高次走査型非線形誘電率顕微鏡法の概念図

図15:SiC-DIMOSFETの断面の6倍波迄の高調波像

図16:典型的なC-V曲線とSiC-DIMOSFETの空乏層の可視化

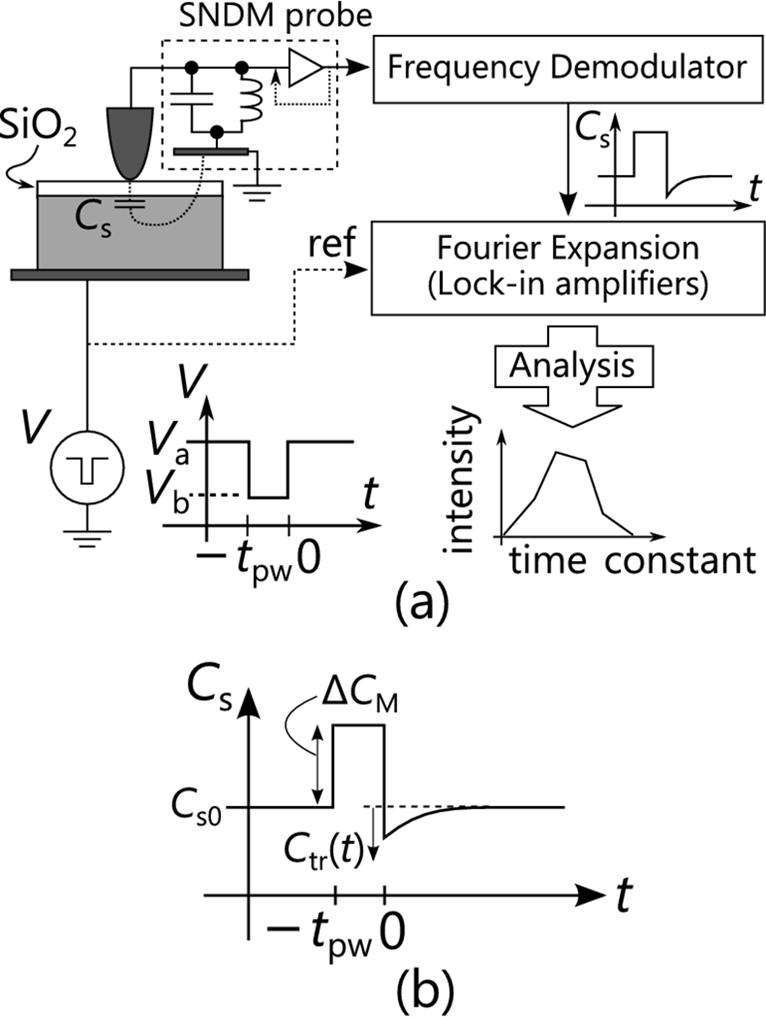

局所DLTS法によるMOS界面トラップの分布計測

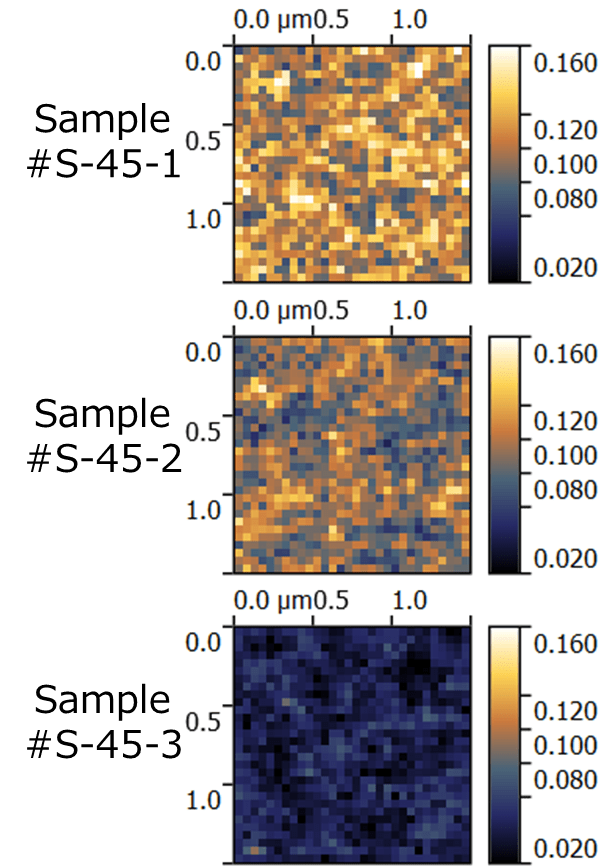

金属-酸化物-半導体(MOS)界面の物理的特性は半導体MOSデバイスの特性に非常に大きな影響を及ぼす。現在までMOS界面の界面順位Ditを計測する方法とHi-Lo法やDLTS法といったMOSキャパシタを基本にした方法が用いられているが、これらの方法はトラップの2次元的な分布計測には適応できない。しかし、現実のトラップは界面近傍で2次元的(場合によっては3次元的)に分布していることは想像に難くなく、不均一な分布がMOS界面移動度低下の原因になっている事も容易に推測できる。そこでMOSキャパシタの上部電極の代わりにSNDMの金属探針を用い局所的にDLTS法の行える局所DLTS法を新規に開発した。(上部電極に極細な探針を用いる事ができるのは単にSNDMの高感度性に因っている。)図17にその原理図を示す。フィリングパルスに反応した過渡静電容量応答をの振幅と減衰の時定数を計測することにより探針直下のDitの大きさとエネルギー深さを知ることができる。本手法を用いて45-nm厚さのSiO2膜を持つシリコン面で4º-off n-型 4H-SiC ウエハーのDit分布を計測した。計測に用いたサンプルは3種類で #S-45-1サンプルはドライ酸化のみのサンプルであり、残り二つのサンプルはNO雰囲気中でPOA処理(post-oxidation annealing) (POA) を行ったものである。POA条件は 1250℃ 10分 (#S-45-2)と 1150℃ 60分 (#S-45-3)であり、もちろんマクロな手法で評価されたDit は#S-45-1が最も高く #S-45-3 が最も低い.図18にこれら三つのサンプルを局所DLTS法で評価した結果を示す。評価したDitの時定数(エネルギー深さに相当)は約1µsecである。これを見ると分かるようにPOAの程度に従ってDitの平均値は小さくなっているが、どの像においてもDitが2次元的に分布している事が良く分かる。このように新開発の局所DLTS法はMOS界面の評価に極めて有効である。

図17:局所DLTS法の原理図。(a)計測系のブロックダイアグラム (b)幅tpwのパルス印加時にティップ直下で起こる理想的な静電容量変化

図18:SiC MOS界面の局所DLTS像(@ τ=1µsec)暗い部分と明るい部分はそれぞれDitの低い領域及び高い領域に相当する

時間分解SNDM (Tr-SNDM)

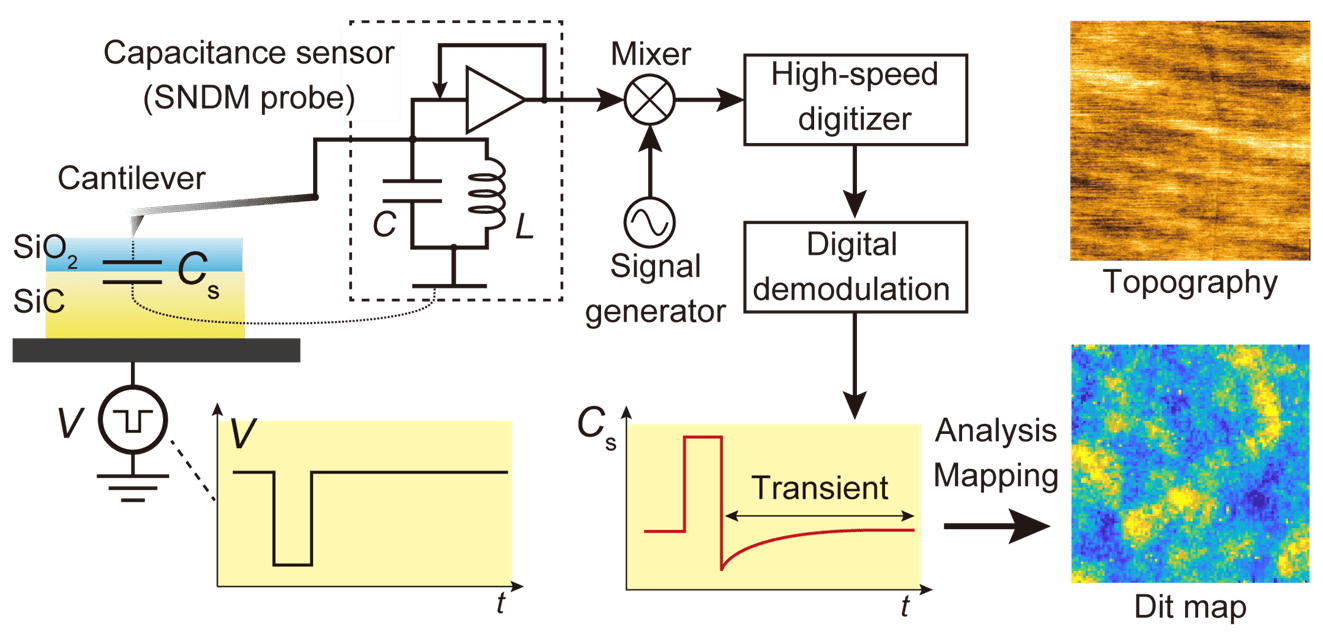

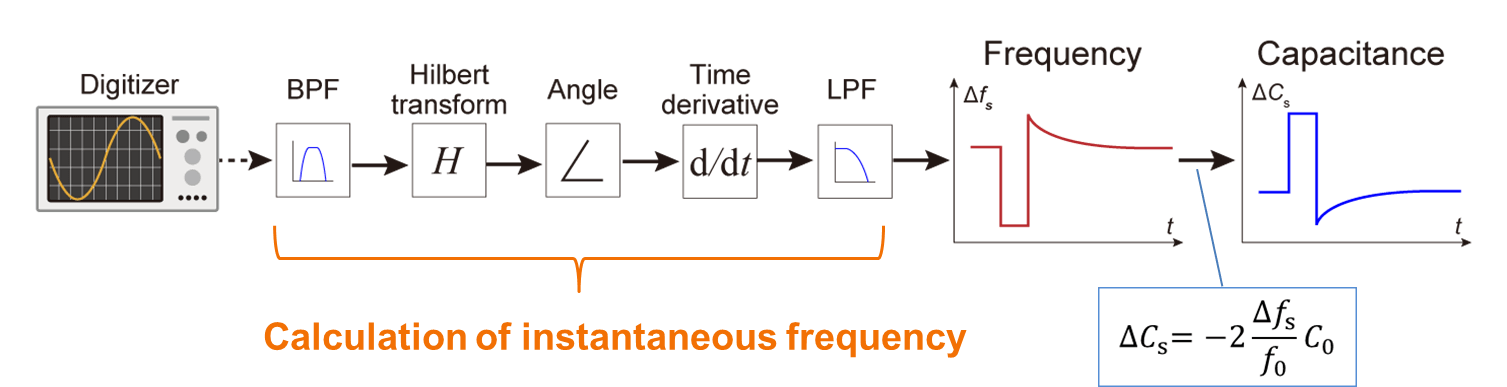

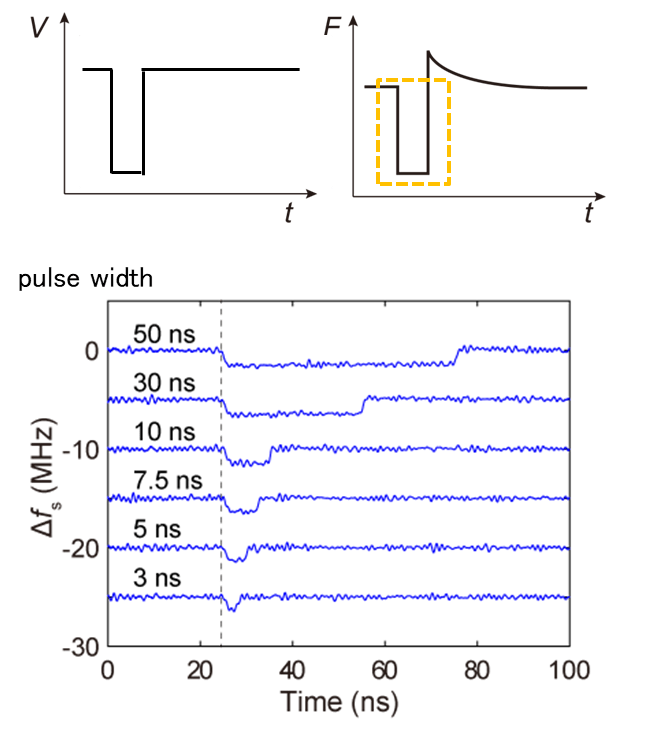

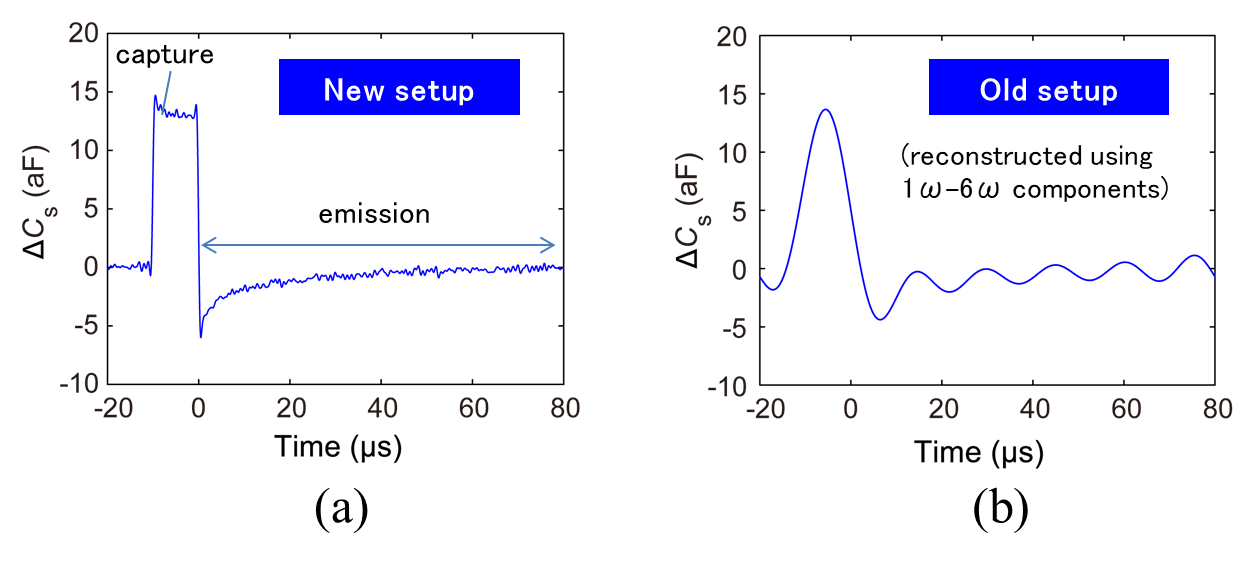

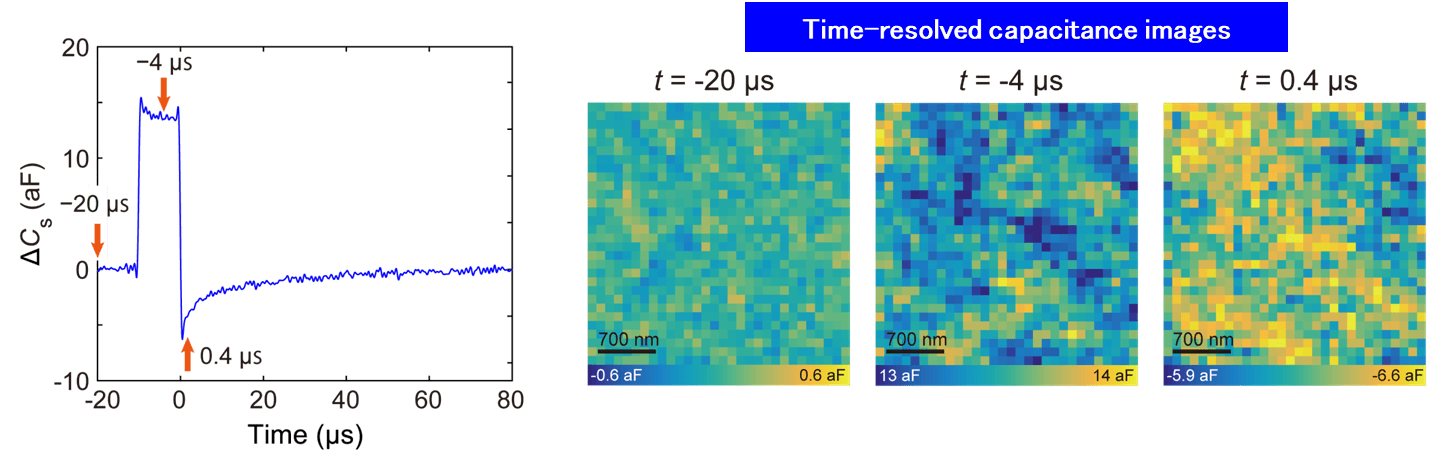

静電容量変化の高速時間分解計測は半導体中の及び界面の欠陥評価に非常に有効である。今回SNDMを用いてナノスケールの空間分解能をもつ時間分解静電容量計測技術を開発した(時間分解SNDM(Tr-SNDM))。SiO2/4H-SiC 界面に加えられた3 nsのパルスに対応した高時間分解静電容量応答の検出に成功した。 更に本Tr-SNDM法を局所DLTS法に適用しSiO2/4H-SiC 界面準位の高時間分解能観測にも成功した。これらの概要を下図19〜24に示す。

図19:時間分解SNDMの概念図

図20:Tr-SNDM法で用いているヒルベルト変換による瞬時数波数の数値計算法

図21:Tr-SNDM法で得られた矩形パルス波形に対する容量変化(周波数変化)の応答波形

図23:容量変化波形の比較. SiO2/SiC サンプルに10 µs 10 Vのフィリングパルスを加えたときの⊿Csの時間変化(a) tr-SNDM法による結果(b) FM復調器とマルチチャネルロックインアンプを用いた従来法による結果

図24:t = -20 µs, t = -4 µs, 及び t = 0.4 µsでの印加パルスに対する静電容量変化㊖Csの2次元像. (t = -20 µs:トラップに電子が捕獲される前なので均一な像、t = -4 µs:捕獲された電子の少ないところに対応した2次元像、t = 0.4 µs:捕獲した電子の濃度に対応する2次元像、t = -4 µsの像と逆コントラストになっている

原子層(2次元)半導体のキャリア分布観察

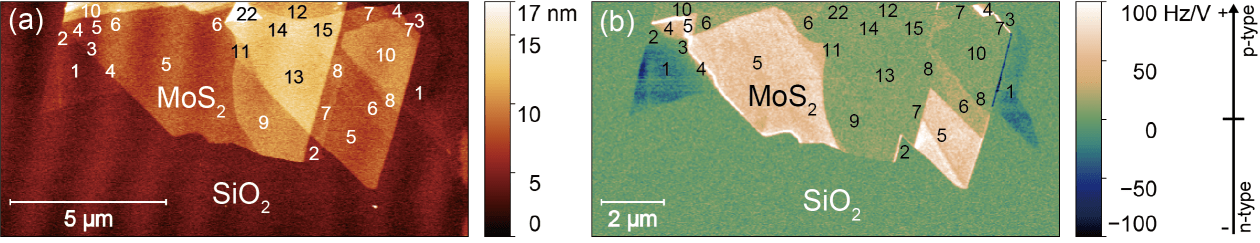

図25:ニオブドープされたSiO2上機械剥離ニ硫化モリブデン(MoS2)のSNDM観察結果 (a) 形状像 (b) SNDM像。像中のアラビア数字は各部の推定された層数を表す。[Reprinted with permission from Fig. 4, J. Appl. Phys. 128, 074301(2020). Copyright 2020 American Institute of Physics]

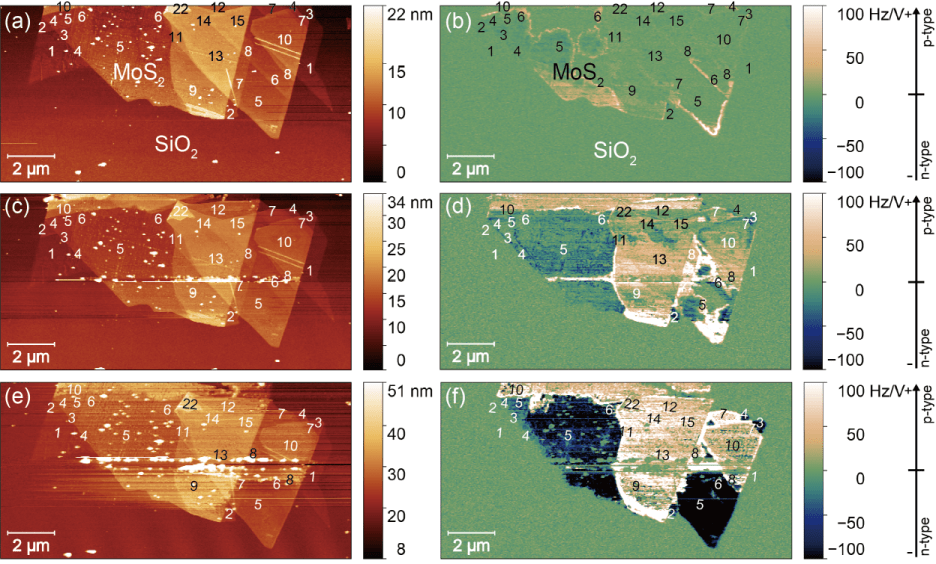

SNDMはシリコンや炭化ケイ素などの半導体に加えて、最近盛んに研究されている原子層(2次元)半導体のキャリア分布観察にも適用可能です。近年、グラフェンなど層状物質を単原子層まで薄くした原子層物質がその特異な物性やそのデバイス応用のため盛んに研究されています。層状物質のなかでも、二硫化モリブデンなど半導体の性質を示す原子層半導体は、次世代の半導体材料として期待されています。上図は熱酸化Si基板上に機械的に剥離したニオブドープMoS2のSNDM像です。ニオブはp型化のためドープされていますが、数原子層以下のニオブドープMoS2がp型半導体としての性質を保持するかは必ずしも自明ではありません。実際、SNDMで観察すると多層部分では確かにp型の多数キャリア(ホール)が検出される一方、単層部分ではn型の多数キャリア(電子)が検出されたことが上図からわかります。詳しい検討結果から、層数が10層以上ではホール密度はほぼ一定ですが、層数が10層を切ると、本来、多数キャリアであったはずのホールの密度が減少しはじめ、2-3層ではほぼ空乏状態に、単層になるとついには電子が多数キャリアになるp型からn型への遷移の様子をSNDM観察で可視化できたことがわかりました。先行研究の結果もふまえると、MoS2の表面に意図せず生じるドナーによって、ニオブドープの効果が減じられ、層数が薄くなると表面からのドーピングがニオブドープの効果を上回って過補償となり、ついにはn型化したものと考えられます。シリコンなどのよく知られる半導体とは異なり、原子層半導体は大変薄いためにその特性はバルクよりも表面や界面の性質に強く左右されるのです。また、同じ試料にUV/オゾン酸化と呼ばれる処理を行うと、下図に示すように、単層だけでなく5層程度の層数を持つ部分まで、さらにn型化が進むことがわかりました。原子層材料を用いたトランジスタなどのデバイスプロセスでは、多数の工程で様々な処理を行うことが考えられますが、各処理が材料のキャリア密度にどのように影響するか、見極めることが必要不可欠です。本結果は、SNDMでは原子層半導体のキャリア分布をナノスケールで評価することが可能なため、原子層半導体デバイスのデバイスプロセスを検証するための有用な手法に成り得ることを示します。

図26:図25と同一試料をUV/オゾン酸化処理した場合のSNDM観察結果。(a), (b) 処理開始10分後 (c), (d) 5分間追加処理後(合計15分間) (e), (f) さらに5分追加処理後(合計20分間)。 (a), (c), (e)は形状像 (b), (d), (f) SNDM像を表す。[Reprinted with permission from Fig. 6, J. Appl. Phys. 128, 074301(2020). Copyright 2020 American Institute of Physics]

3次元フラッシュメモリ内の電子とホールの分布のSNDMによる観察

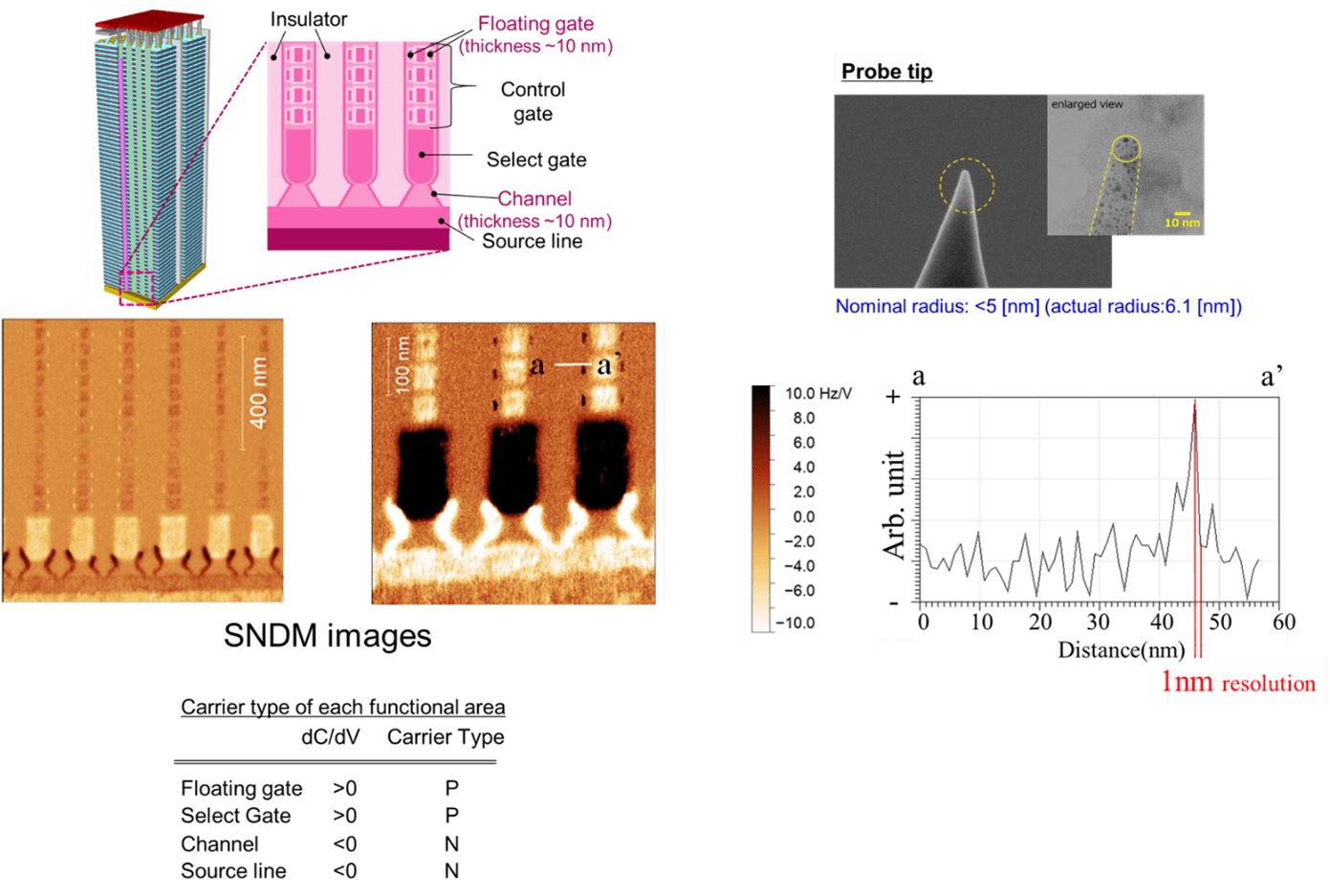

最新のフラッシュメモリは3次元(3D)構造を取ることによって、記憶容量を増大させています。ここではサイズが10 [nm]未満の3Dフラッシュメモリセルのフローティングゲートおよびチャネル構造のキャリア分布は、走査型非線形誘電体顕微鏡(SNDM)を使用して明確に測定された結果をご紹介します。半径5nmの非常に鋭いダイヤモンドチップを使用して最高の空間分解能を達成し、背景とのコントラスト差の大きいフローティングゲートのSNDM信号を取得することに成功しました。最小空間分解能を推定し、SNDMが1.9 [nm]未満の空間分解能を示すことを確認しました。さらに、チャネル間のn型不純物の拡散長の差(作製誤差)が21 [nm]未満であるという明確な証拠をつかみました。これらの結果は、最新の極微小なデバイスのパフォーマンスの最適化とデバイスの故障解析にとって非常に有効な方法を確立することに成功したことを意味します。

文献

- K. Honda, K. Ishikawa, and Y. Cho: J.Phys.: Conf. Ser. 209 (2010) 012050

- N. Chinone and Y. Cho: IEEE Transactions on Electron Devices 63 (2016) 3165

- K. Hirose, Y. Goto, N. Chinone, and Y. Cho: Jpn. J. Appl. Phys 55 (2016) 08NB13

- K. Hirose, K. Tanahashi, H. Takato, and Y. Cho: Appl. Phys. Lett. 111 (2017) 032101

- N. Chinone and Y. Cho: J. Appl. Phys. 122 (2017) 105701

- Y. Yamagishi and Y. Cho: Appl. Phys. Lett. 111 (2017) 163103

- K. Yamasue and Y. Cho: Appl. Phys. Lett. 112 (2018) 243102

- J. Hirota, K. Yamasue, and Y. Cho: Microelectronics Reliability 114 (2020) 113774